|

|

|

|

(点击题目可以在互联网中搜索该题目的相关内容)

日期:2007-9-21 20:07:06 来源: 作者: 点击: |

点击【 大 中 小 】,可以选择字体的大小,以便你阅读.

|

来源:EE Times

he successful development of embedded systems requires the continuous integration of hardware and firmware throughout all stages of the project. Transaction-level simulation aids in architecture development and refinement, but lacks the detail necessary to confirm that the memory subsystem can support the reset and boot-up process.

嵌入式系统的成功开发需要在项目的所有阶段不断地将硬件和固件结合起来。事务级仿真可以帮助发展和精炼体系结构,但是它不能详细地证实内存子系统能够支持重启和启动处理。

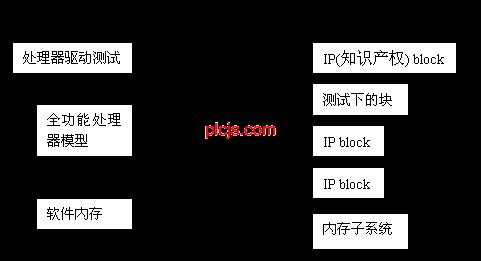

执行固件能阻止寄存器传送级硬件描述以验证启动成功,并且阻止适当配置的实时操作系统硬件适配层。所有直接连接到总线的IP(知识产权)blocks应该由在周期精确的CPU上执行的处理器驱动测试来验证。在tapeout(完成设计支付制造)之前,需要使用精确签核(signoff)的处理器模型将管脚级、时序精确的总线事务与所有的主从总线相交换。当处理器驱动测试运行于第一块硅片上时,在虚拟环境中验证这些测试将会变得轻松。

在所有这些验证阶段中,软件维持一种单个抽象级,而硬件描述则从事务级延伸至门级和物理实现级。理想的情况是,延伸此连续统一体的工具应该给出用于执行硬件和固件的相容的图形用户界面(GUI)和调试环境。在每一抽象级,硬件/固件的协同发展都会有一些利益的权衡,但是满足一些特定的需求会产生相似的仿真和调试环境。

把嵌入式核作为一种将读写总线周期加入到IP寄存器的工具对于基于HDL(硬件描述语言)的测试平台来说是个显著的帮助。作为功能验证的正交方法,处理器驱动测试可以给出HDL测试平台可能忽略的总线接口和时序误差。这些测试易于编写,具有很强的可移植性,在所有抽象级上工作良好,并且可以运行于硅片上。作为手工编写测试的补充,验证组可以采用大段的来自于固件组的代码。引导代码、硬件诊断和RTOS(实时操作系统)硬件适配层或板级支持包与硬件设计的功能验证紧密相关。

测试可移植性

嵌入式代码是个名副其实的可移植性测试平台。只要地址映射在整个硬件设计过程中保持一致,用C语言或汇编语言编写的并且经过编译后运行于处理器上的测试程序就可以使用于模块、子系统、芯片和系统级上,也能运行于物理原型上。没有其他测试平台语言或测试平台工具能够做到这一点。

处理器驱动测试程序的可移植性背后的神秘之处在于其设计细节的独立性。测试程序简单地将数据读取或写入到特定的寄存器或内存地址上。只要此地址在处理器的线性地址空间(地址映射)位置保持不变,测试程序就不必依靠实际的传输机制。单个测试程序不用改变一行源代码就可以容纳大量的硬件变量:

•总线实现:总线周期可以是具有详细时序的管脚级的或是高级的事务。处理器模型规定了插入每个总线周期的详细级别。

•硬件描述:硬件可以在硅片上的寄存器传送级、门级或实现级事务上建模。只要在设计中硬件描述可以将读写操作传递到正确的寄存器中,测试程序就不用在乎完成交互的具体的仿真级别。

• 内存:内存子系统可以很详细地实现(flash,DDR2)或者抽象为简单的阵列。通常,内存子系统不在模块级出现。先进的联合仿真工具允许使用者声明内存参考和用于程序存储、堆栈的内存空间。在子系统级,不用改变模块级测试程序就能引入详细的内存模型。务必要增加代码来配置内存管理单元,但是,一旦配置了模块,测试程序将会毫无变化地运行。

用C语言或汇编语言编写的并且编译至目标的测试程序能够以极不同的速度运行,这取决于硬件平台如何实现。对于门级签核(signoff)仿真,运行速度从真实目标上的实时速度到每秒大约一个模块。

图片来源:Mentor图像公司

同样的模块级测试可以用于整个验证过程中。其他模块和内存子系统的变化对此测试不起作用。

处理器模型

许多处理器驱动测试程序的可移植性是由具有大量抽象级别和性能的处理器模型所引起的。这些模型是测试程序和目标硬件之间的接口。对于测试这方面,所有模型具有一致的观点,就是说,它们具有将C语言或汇编语言编译成可执行的形式的能力。这种能力使得相同的测试程序能够运行于一系列的处理器模型和真实目标上。

正是硬件的内部细节和接口将这些处理器模型分成了大量的类别:

• 事务级:快速,拥有总线事务接口;速度从每秒百万条指令到每秒千万条指令。Cache(高速缓冲存储器)和流水线不用建模。实质上,这些是具有连接硬件的事务级接口的指令集仿真器。这种方法的强势在于其速度快,而其弱点是需要事务级硬件描述,通常情况下若没有付出额外努力此描述不能实现。

•周期精确性:具有管脚级总线接口的合理的速度。“周期精确”意味着cache和流水线建立了模型。这些模型对硅片产生同样的总线周期,伴随着流水线预取和 cache填充突发读取的精确建模。周期可能不会随精确的时钟边缘时序发生,但是时钟边缘的行为应该精确。速度从每秒五千个到五十万个指令。这种方法的强势在于它有不用设计模型和周期精确就能进行RTL(寄存器传送级)描述的能力。但是其执行性能要比实时速度慢上几个数量级。

•签退(signoff)精确:高精确性但是非常慢,这些模型通常直接来自于用于合成硅片的RTL,所以它们应该能够精确匹配物理核。其强势是精确性,弱势是仿真速度只有大约每秒一个模块。

•真实目标:就是硅片本身,它可以精确定义并且以实时执行速度完成性能。主要的缺点是需要物理原型,并且缺乏硬件调试的可见性。此方法通常使用于设计周期的末期。

处理器驱动测试程序延伸虚拟仿真和物理原型的能力带来了许多好处。引入第一个硅片一般是个紧张的过程,因为有许多未知因素,大家似乎都抱观望态度。在硅片上进行测试程序的预验证消除了主要的未知因素。因为处理器测试不用建模就能延伸虚拟域和物理域,所以设计时在tapeout(完成设计支付制造)之前引入了可以进行仿真和调试的处理器。这种方法消除了典型的由于物理原型而带来的设计和测试误差,并提高了相当轻松地启动第一个硅片的信心。

同样的,真实目标测试的覆盖级最多也只是个猜测。然而,由于准确的测试可以仿真运行和在硅片上运行,所以虚拟测试度量如代码覆盖和断言覆盖能够评估真实目标测试的完整性。精确的度量使人们相信物理原型已经经过了充分的证实。

物理原型具有明显的快速性和高精确性,但是由于硬件可见性的限制,它难以进行对逻辑错误的调试。由于它们的可移植性,在真实目标上运行失败的处理器驱动测试程序可以轻松地进行仿真运行,同时具有极好的调试可见性和控制性。经过实验室里两个星期的调试仍未被解决的问题在一个小时的仿真再运行中就被诊断和修正了。

因为处理器驱动测试程序可以应用于大范围的验证方法,所以需要注意避免过多的执行和调试环境。在硬件方面,先进的仿真器将连续体从事务级 SystemC延伸到门级签退(signoff)。它们给出一组常用的窗口用于调试这些不同的硬件描述。

为了调试处理器驱动测试自身的C或汇编代码,需要一个源级软件调试器。与逻辑仿真器GUI不同的是,源调试器趋向于紧密连接处理器模型。例如,用于事务级模型的源级调试器可能与用于同样嵌入式核的周期精确模型截然不同。因为这些模型用C语言编写,所以它们通常将调试器API合并到服务调试器用于显示处理器状态、寄存器信息和接受用户发出的暂停、运行和单步执行命令。通过连接到JTAG端口的硬件探点,源级调试器也可以和真实目标一起使用。

当用于事务的单个硬件调试环境达到门级时,寻找一个统一的调试处理器驱动测试自身的方案变得更为困难——这种奇怪的事情在假设测试源保持不变而调试环境变化的情况下发生。

随着处理器驱动测试成为功能性验证的集成组件,我们有理由希望逻辑仿真器GUI将会包括源级调试。在这种GUI中,不同的窗口显示运行于处理器的代码和HDL源调试代码,这使以嵌入式代码作为测试平台的硬件验证工程师更为轻松。

关于作者:

Jim Kenney(im_kenney@mentor.com)是Mentor图像公司系统级部门的产品市场经理。他获得了克莱姆森(Clemson)大学的电机工程硕士(BSEE)学位。

| |

摘自中国工控网

上一篇: 车载嵌入式系统开发的新解决方案

下一篇: 用于嵌入式机器控制的CAN总线 |